TOIREX

ETR0706-013

### 2 channel Synchronous Step-Down DC/DC Converter with Manual Reset

### ■ GENERAL DESCRIPTION

The XC9515 series consists of 2 channel synchronous step-down DC/DC converters and a voltage detector with delay circuit built-in. The DC/DC converter block incorporates a P-channel  $0.35\Omega$  (TYP.) driver transistor and a synchronous N-channel  $0.35\Omega$  (TYP.) switching transistor. By minimizing ON resistance of the built-in transistors, the XC9515 series can deliver highly efficient and a stable output current up to 800mA. With high switching frequencies of 1MHz, a choice of small inductor is possible.

The series has a built-in UVLO (under-voltage lock-out) function, therefore, the internal P-channel driver transistor is forced OFF when input voltage becomes 1.8V or lower (for XC9515A, 2.7V or lower).

The voltage detector block can be set delay time freely by connecting an external capacitor. With the manual reset function, the series can output a reset signal at any time.

### APPLICATIONS

- OVDs

- Blue-ray Disk

- ●LCD TVs, LCD modules

- Multifunctional printers

- Photo printers

- Set top boxes

### ■FEATURES

| DC/DC                 |                                       |

|-----------------------|---------------------------------------|

| Input Voltage Range   | : 2.5V ~ 5.5V                         |

| Output Voltage        | : V <sub>OUT1</sub> =1.2V ~ 4.0V      |

|                       | V <sub>OUT2</sub> =1.2V~ 4.0V         |

|                       | (Accuracy ±2%)                        |

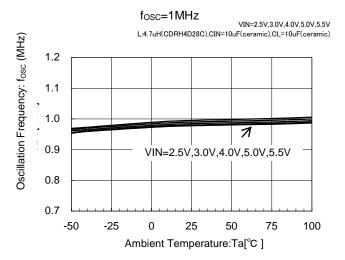

| Oscillation Frequency | : 1MHz (Accuracy ±15%)                |

| High Efficiency       | : 95% (VIN=5V, VOUT=3.3V)             |

| Output Current        | : 800mA                               |

| Control               | : PWM control                         |

| Protection Circuits   | : Thermal Shutdown                    |

|                       | : Integral Latch (Over Current Limit) |

|                       | : Short Protection Circuit            |

Ceramic Capacitor Compatible

#### Voltage Detector (VD)

| Detect Voltage Range     | : 2.0V ~ 5.5V (Accuracy ±2%) |

|--------------------------|------------------------------|

| Delay Time               | : 173ms                      |

|                          | (When Cd=0.1µF is connected) |

| Output Configuration     | : N-channel open drain       |

| Package                  | : QFN-20                     |

| Environmentally Friendly | : EU RoHS Compliant, Pb Free |

|                          |                              |

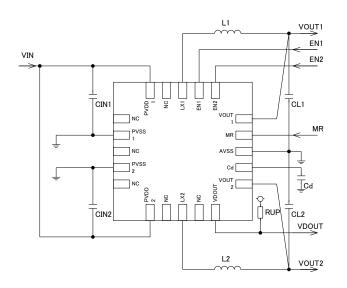

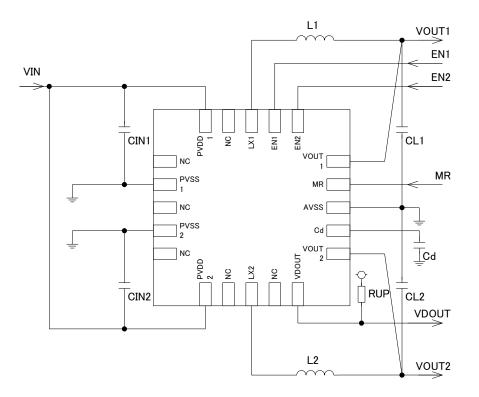

# TYPICAL APPLICATION CIRCUIT

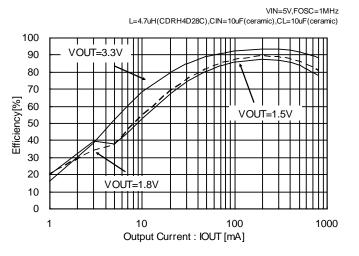

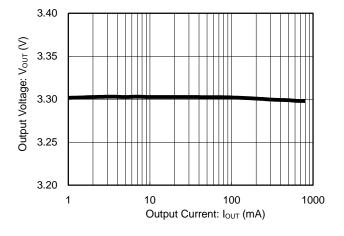

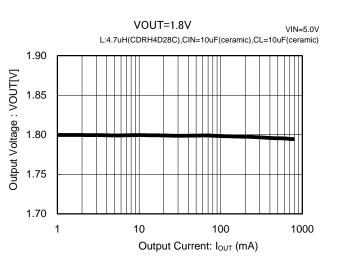

### TYPICAL PERFORMANCE CHARACTERISTICS

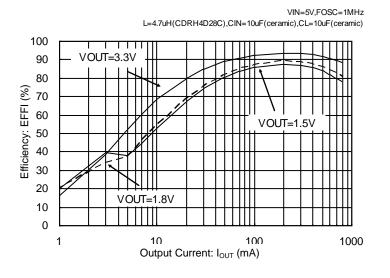

Efficiency vs. Output Current

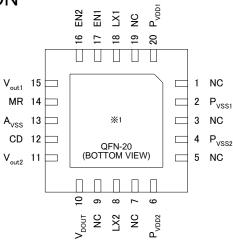

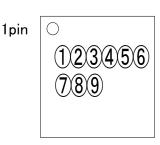

## ■ PIN CONFIGURATION

## ■ PIN ASSIGNMENT

| PIN<br>NUMBER | PIN NAME           | FUNCTION                | PIN<br>NUMBER | PIN NAME          | FUNCTION                   |

|---------------|--------------------|-------------------------|---------------|-------------------|----------------------------|

| 1             | NC                 | No Connection           | 11            | V <sub>OUT2</sub> | Output Voltage Sense 2     |

| 2             | P_V <sub>SS1</sub> | Power Ground 1          | 12            | Cd                | Delay Capacitor Connection |

| 3             | NC                 | No Connection           | 13            | $A_V_{SS}$        | Analog Ground              |

| 4             | $P_V_{SS2}$        | Power Ground 2          | 14            | MR                | Manual Reset               |

| 5             | NC                 | No Connection           | 15            | V <sub>OUT1</sub> | Output Voltage Sense1      |

| 6             | $P_V_{DD2}$        | Power Supply 2          | 16            | EN2               | CH2 ON/OFF Control         |

| 7             | NC                 | No Connection           | 17            | EN1               | CH1 ON/OFF Control         |

| 8             | LX2                | Switching Output 2      | 18            | LX1               | Switching Output 1         |

| 9             | NC                 | No Connection           | 19            | NC                | No Connection              |

| 10            | V <sub>DOUT</sub>  | Voltage Detector output | 20            | $P_V_{DD1}$       | Power Supply 1             |

\*1 Back metal pad voltage  $\,:\, V_{\text{SS}}$  level

(The back metal pad should be soldered to enhance mounting strength and heat release. If the pad needs to be connected to other circuit, care should be taken for the pad voltage level)

### ■ FUNCTION CHART

●EN1, EN2 and MR pins are internally pulled up. \*2)

| <b>D</b> 111 |            |                                   |

|--------------|------------|-----------------------------------|

| PIN          | LEVEL      | OPERATIONAL STATUS                |

| EN1          | High, Open | DC/DC_CH1 Operation               |

|              | Low        | DC/DC_CH1 Stop                    |

| EN2          | High, Open | DC/DC_CH2 Operation               |

| EINZ         | Low        | DC/DC_CH2 Stop                    |

| MR           | High, Open | VD_OUT Detect RESET Signal Output |

| MR           | Low        | VD_OUT Force RESET Signal Output  |

EN1, EN2 and MR pins are internally pulled up so that the levels of High and Open are same function.

●EN1, EN2 and MR pins are left open internally. \*2)

| PIN   | LEVEL | OPERATIONAL STATUS                |  |  |

|-------|-------|-----------------------------------|--|--|

| EN1   | High  | DC/DC_CH1 Operation               |  |  |

| EINT  | Low   | DC/DC_CH1 Stop                    |  |  |

| EN2   | High  | DC/DC_CH2 Operation               |  |  |

| EINZ  | Low   | DC/DC_CH2 Stop                    |  |  |

| MR    | High  | VD_OUT Detect RESET Signal Output |  |  |

| IVITS | Low   | VD_OUT Force RESET Signal Output  |  |  |

EN1, EN2 and MR pins are floated inside so that these pins shall not be left open outside.

\*2) Please refer to the PRODUCTION CLASSIFICATION to see the combination of pull-up status regarding the EN1, EN2, and MR pins.

### ■ PRODUCT CLASSIFICATION

Ordering Information (Standard products)

XC9515123456-7<sup>(\*1)</sup>

| DESIGNATOR | DESCRIPTION                             | SYMBOL | DESCRIPTION                                             |

|------------|-----------------------------------------|--------|---------------------------------------------------------|

|            |                                         | А      | Input Voltage Range 5V±10%, UVLO Voltage 2.7V (TYP.)    |

| 1)         | Input Voltage & UVLO                    | В      | Input Voltage Range 2.5V~5.5V, UVLO Voltage 1.8V (TYP.) |

|            |                                         | A      | EN1, EN2, MR pins are not pulled up internally          |

|            |                                         | В      | EN1, EN2 pins have built-in pull-up resistors,          |

|            | EN & MR logic control conditions        | Б      | MR pin has a built-in pull-up resistor                  |

| 2          |                                         | С      | EN1, EN2 Pins are not pulled up internally,             |

|            |                                         | C      | MR pin has a built-in pull-up resistor                  |

|            |                                         | D      | EN1, EN2 pins have built-in pull-up resistors,          |

|            |                                         | D      | MR pin are not pulled up internally                     |

| 34         | 3 4 Set Voltage Combinations            |        | Based on Torex Standard Product Number                  |

| 56-7       | Packages<br>Taping Type <sup>(*2)</sup> | ZR-G   | QFN-20 (1,000pcs/Reel)                                  |

(\*1) The "-G" suffix indicates that the products are Halogen and Antimony free as well as being fully RoHS compliant.

(<sup>\*2)</sup> The device orientation is fixed in its embossed tape pocket. For reverse orientation, please contact your local Torex sales office or representative. (Standard orientation: (SR-⑦), Reverse orientation: (SL-⑦)

| XC95151234 | VOUT1 [V] | VOUT2 [V] | VDF(Detect Voltage) [V] |

|------------|-----------|-----------|-------------------------|

| XC9515AB02 | 1.2       | 3.3       | 3.5                     |

| XC9515AB04 | 1.5       | 3.3       | 3.5                     |

| XC9515AB05 | 1.8       | 3.3       | 3.5                     |

| XC9515BA06 | 1.2       | 1.8       | 3.0                     |

| XC9515AA07 | 1.2       | 3.3       | 4.2                     |

| XC9515AA08 | 3.3       | 1.8       | 4.5                     |

About 1234 (Output Voltage, Detect Voltage)

\*This series are semi-custom products. For other combinations, output voltages, detect voltage and etc., please ask Torex sales contacts.

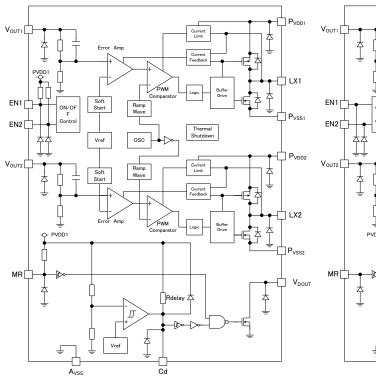

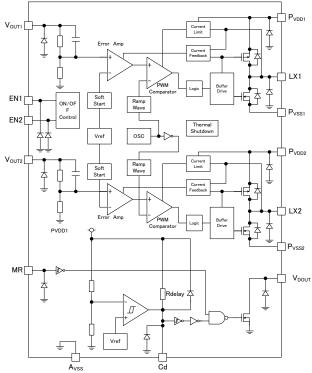

### ■BLOCK DIAGRAM

#### ●EN1 Pin, EN2 Pin, MR Pin, Pull-up Inside

### ■ABSOLUTE MAXIMUM RATINGS

Ta=25°C

| PARAMETER                                |              | SYMBOL                                          | RATINGS                                             | UNITS            |      |

|------------------------------------------|--------------|-------------------------------------------------|-----------------------------------------------------|------------------|------|

| $P_V_{DD1} \cdot P_V_{DD2} F$            | Pin Voltage  | $P_V_{DD1}, P_V_{DD2}$                          | A_V <sub>SS</sub> -0.3 ~ 6.5                        | V                |      |

| V <sub>OUT1</sub> •V <sub>OUT2</sub> Pir | n Voltage    | V <sub>OUT1</sub> , V <sub>OUT2</sub>           | A_V <sub>SS</sub> -0.3 ~ 6.5                        | V                |      |

| Cd Pin Vol                               | tage         | V <sub>Cd</sub>                                 | A_V <sub>SS</sub> -0.3 ~ P_V <sub>DD1·2</sub> + 0.3 | V                |      |

| V <sub>DOUT</sub> Pin V                  | oltage       | V <sub>DOUT</sub>                               | A_V <sub>SS</sub> -0.3 ~ 6.5                        | V                |      |

| V <sub>DOUT</sub> Pin Current            |              | I <sub>DOUT</sub>                               | 10                                                  | mA               |      |

| EN1•EN2•MR F                             | vin Voltage  | $V_{\text{EN1}}, V_{\text{EN2}}, V_{\text{MR}}$ | A_V <sub>SS</sub> -0.3 ~ 6.5                        | V                |      |

| LX1 · LX2 Pin                            | Voltage      | V <sub>Lx1</sub> , V <sub>Lx2</sub>             | A_V <sub>SS</sub> -0.3 ~ P_V <sub>DD1·2</sub> +0.3  | V                |      |

| LX1 · LX2 Pin                            | Current      | I <sub>Lx1</sub> , I <sub>Lx2</sub>             | 1500                                                | mA               |      |

| Dower Dissinction                        | ation QFN-20 | Pd (Free air)                                   | 300                                                 | mW               |      |

| Power Dissipation                        |              | QFN-20                                          | QFN-20                                              | Pd (PCB mounted) | 1000 |

| Operating Temperature Range              |              | Topr                                            | -40 ~ 85                                            | °C               |      |

| Storage Tempera                          | ture Range   | Tstg                                            | -55 ~ 125                                           | °C               |      |

\*  $P_V_{DD1 \cdot 2}$  stands for  $P_V_{DD1}=P_V_{DD2}$

$A\_V_{SS} = P\_V_{SS1} = P\_V_{SS2} = 0V$

#### ●EN1 Pin, EN2 Pin, MR Pin, internally floating

## ELECTRICAL CHARACTERISTICS

#### XC9515AB04xx

| PARAMETER                         | SYMBOL                              | CONDITIONS                                                                                                                                            | MIN.             | TYP.               | MAX.                | UNITS | CIRCUIT |

|-----------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|---------------------|-------|---------|

| Input Voltage                     | Vin                                 |                                                                                                                                                       | 4.5              | 5.0                | 5.5                 | V     | _       |

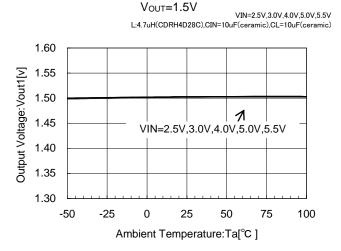

| Output Voltage 1                  | Vout1                               | Connected to the external components, $P_V_{DD1\cdot2}=V_{EN1}=V_{EN2}=0V$ , $I_{OUT1}=30mA$                                                          | 1.470            | 1.500              | 1.530               | V     | 1       |

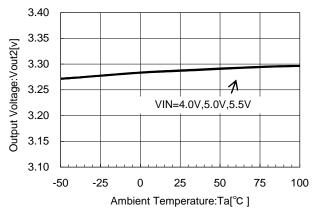

| Output Voltage 2                  | Vout2                               | Connected to the external components, $P_V_{DD1\cdot2}=V_{EN2}=V_{EN1}=0V$ , $I_{OUT2}=30mA$                                                          | 3.234            | 3.300              | 3.366               | V     | 1       |

| Maximum Output Current 1 • 2 (*1) | IOUTMAX1<br>IOUTMAX2                |                                                                                                                                                       | 800              | -                  | -                   | mA    | 1       |

| Current Limit 1 • 2               | Ilim1,<br>Ilim 2                    |                                                                                                                                                       | 1000             | -                  | -                   | mA    | 2       |

| Oscillation Frequency             | f <sub>osc</sub>                    | Connected to the external components, $I_{\text{OUT}}$ =10mA                                                                                          | 0.85             | 1.00               | 1.15                | MHz   | 1       |

| Maximum Duty Cycle                | D <sub>MAX</sub>                    | V <sub>OUT1</sub> =V <sub>OUT2</sub> =0V                                                                                                              | 100              | -                  |                     | %     | 2       |

| Minimum Duty Cycle                | D <sub>MIN</sub>                    | V <sub>OUT1</sub> =V <sub>OUT2</sub> =V <sub>IN</sub>                                                                                                 | -                | -                  | 0                   | %     | 2       |

| Efficiency 1 (*2)                 | EFFI1                               | Connected to the external components,<br>$P_V_{DD1\cdot2}=V_{EN1}=5.0V$ , $V_{EN2}=0V$ ,<br>$V_{OUT1}=1.5V$ , $I_{OUT}1=200mA$                        | -                | 89                 | -                   | %     | 1       |

| Efficiency 2 (*2)                 | EFFI2                               | Connected to the external components,<br>$P_V_{DD1\cdot2}=V_{EN2}=5.0V$ , $V_{EN1}=0V$ ,<br>$V_{OUT2}=3.3V$ , $I_{OUT2}=200mA$                        | -                | 94                 | -                   | %     | 1       |

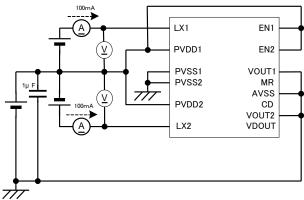

| LX1·2 "H" ON Resistance           | Rlx1h•Rlx2h                         | $V_{OUT1}=V_{OUT2}=0V$ , ILx1=ILx2=100mA (*3)                                                                                                         | -                | 0.35(*4)           | -                   | Ω     | 3       |

| LX1-2 "L" ON Resistance           | RLX1L·RLX2L                         |                                                                                                                                                       | -                | 0.35(*4)           | -                   | Ω     |         |

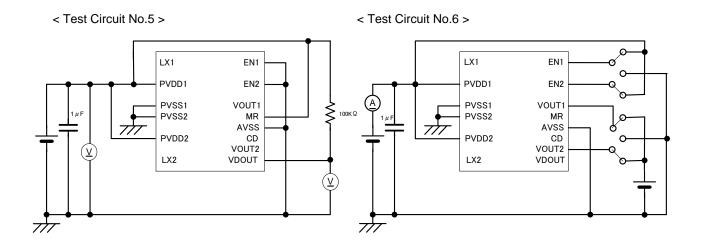

| Integral Latch Time 1·2           | $t_{LAT1}, t_{LAT2}$                | LX1 and LX2 are pulled down by a resistor of $200 \Omega$<br>$V_{OUT1}$ =Setting Voltage × 0.9,<br>$V_{OUT2}$ = Setting Voltage × 0.9 <sup>(*5)</sup> | -                | 6                  | -                   | ms    | 7       |

| Soft-Start Time 1 • 2             | t <sub>SS1</sub> , t <sub>SS2</sub> | Time until EN1, EN2 or both pins changes from 0V to $V_{IN}$ and voltage becomes $V_{OUT1\cdot2} \times 0.95$ , $I_{OUT1\cdot2}=10mA$                 | -                | 1.3                | -                   | ms    | 1       |

| EN1·2 "H" Level Voltage           | Ven1h,<br>Ven2h                     | V <sub>OUT1</sub> =V <sub>OUT2</sub> =0V<br>Voltage which LX1 or LX2 becomes "H" <sup>(*6)</sup>                                                      | 1.2              | -                  | V <sub>IN</sub>     | V     | 4       |

| EN1·2 "L" Level Voltage           | Ven1l,<br>Ven2l                     | V <sub>OUT1</sub> =V <sub>OUT2</sub> =0V<br>Voltage which LX1 or LX2 becomes "L" <sup>(*6)</sup>                                                      | AV <sub>SS</sub> | -                  | 0.4                 | V     | 4       |

| EN1-2 "H" Level Current           | Ien1h, Ien2h                        | P_V <sub>DD1.2</sub> =V <sub>EN1</sub> =V <sub>EN2</sub> =5.5V                                                                                        | -                |                    | 0.1(*8)             | μA    | 4       |

| EN1-2 "L" Level Current           | IEN1L, IEN2L                        | $P_V_{DD1\cdot 2}=5.5V, V_{EN1}=V_{EN2}=0V$                                                                                                           | -                | -6 <sup>(*8)</sup> | -                   | μA    | 4       |

| LX1·2 "H" Leakage Current (*7)    | Ileak1h,<br>Ileak2h                 | $P_V_{DD1} = V_{LX1} = V_{LX2} = 5.5V, V_{EN1} = V_{EN2} = 0V$                                                                                        | -                | -                  | 1.0 <sup>(*9)</sup> | μA    | 4       |

| LX1·2 "L" Leakage Current         | Ileak1l,<br>Ileak2l                 | $P_V_{DD1-2}$ =5.5V, $V_{LX1}$ = $V_{LX2}$ = $V_{EN1}$ = $V_{EN2}$ =0V                                                                                | -3.0(*9)         | -                  | -                   | μA    | 4       |

Test Conditions :

\*  $P_V_{DD1 \cdot 2}$  stands for  $P_V_{DD1}=P_V_{DD2}$

\*\*Unless otherwise stated,  $P_V_{DD1}$ . 2=5V,  $V_{EN1}$ = $V_{EN2}$ =  $P_V_{DD1}$ . 2 \*\*\*  $A_V_{SS}$ = $P_V_{SS1}$ = $P_V_{SS2}$ =0V

NOTE :

- \*1 : When the difference between the input and the output is small, some cycles may be skipped completely before current maximizes. If current is further pulled from this state, output voltage will decrease because of P-ch driver ON resistance.

- \*2 : EFFI = { ( output voltage x output current ) / ( input voltage x input current) } x 100

- \*3 : On resistance ( $\Omega$ )= (V<sub>IN</sub> Lx pin measurement voltage) / 100mA

\*4 : Designed value.

- \*5 : Time until it short-circuits LX1 (LX2 in the side of 2CH) with GND via 1Ωof resistor from an operational state and is set to Low level from current limit pulse generating.

- \*6 : "H" is judged as "H">V<sub>IN</sub>-0.1V, "L" is judged as "L"<0.1V.

- \*7 : When temperature is high, a current of approximately  $20\mu A$  (maximum) may leak.

- \*8 : Current which EN1 and EN2 are measured separately.

- \*9 : Lead current which LX1 and LX2 are measured separately.

# ELECTRICAL CHARACTERISTICS (Continued)

XC9515AB04xx

#### Voltage Detector (VD) (MP nin Bull un Incide) Block

| ●Voltage Detector (VD) (MR pin Pull-up Inside) Block Ta=25° |                         |                                                                  |                  |                        |                  |       |         |  |

|-------------------------------------------------------------|-------------------------|------------------------------------------------------------------|------------------|------------------------|------------------|-------|---------|--|

| PARAMETER                                                   | SYMBOL                  | CONDITIONS                                                       | MIN.             | TYP.                   | MAX.             | UNITS | CIRCUIT |  |

| Detect Voltage                                              | V <sub>DF(E)</sub> (*1) |                                                                  | VDF(T)<br>× 0.98 | Vdf(t) <sup>(*2)</sup> | VDF(T)<br>× 1.02 | V     | 5       |  |

| Hysteresis Width                                            | V <sub>HYS</sub>        | $V_{HYS}=(V_{DR(E)})^{(3)} - V_{DF(E)} / V_{DF(E)} \times 100$   | -                | 5.0                    | -                | %     | -       |  |

| VD Output Current                                           | I <sub>DOUT</sub>       | $P\_V_{DD1\cdot2}=V_{DF}\text{-}0.01V,$ Apply 0.5V to $V_{DOUT}$ | 5.0              | 6.6                    | 8.0              | mA    | 4       |  |

| Delay Resistance                                            | R <sub>DLY</sub>        |                                                                  | -                | 2.5                    | -                | MΩ    | -       |  |

| MR "H" Level Voltage                                        | V <sub>MRH</sub>        | V <sub>DOUT</sub> ="H" Level Voltage (*3)                        | 1.2              | -                      | V <sub>IN</sub>  | V     | 4       |  |

| MR "L" Level Voltage                                        | V <sub>MRL</sub>        | V <sub>DOUT</sub> ="L" Level Voltage (*3)                        | AV <sub>SS</sub> | -                      | 0.4              | V     | 4       |  |

| MR "H" Level Current                                        | I <sub>MRH</sub>        | $P_V_{DD1\cdot 2}=V_{MR}=5.5V$                                   | -                | -                      | 0.1              | μA    | 4       |  |

| MR "L" Level Current                                        | I <sub>MRL</sub>        | $P_V_{DD1\cdot_2}=5.5V, V_{MR}=0V$                               | -                | -6.0                   | -                | μA    | 4       |  |

Test Conditions :

\*  $P_V_{DD1}$  · 2 stands for  $P_V_{DD1}=P_V_{DD2}$

\*\*Unless otherwise stated,  $P_V_{DD1 \cdot 2}$ =5V,  $V_{EN1}$ = $V_{EN2}$ =  $P_V_{DD1 \cdot 2}$ \*\*\* A\_V<sub>SS</sub>=P\_V<sub>SS1</sub>=P\_V<sub>SS2</sub>=0V

NOTE :

\*1 : V<sub>DF(E)</sub>=Detect Voltage

\*2 : V<sub>DR(E)</sub>=Release Voltage

\*3 : "H" is judged as "H">V\_IN-0.1V, "L" is judged as "L"<0.1V

#### XC9515AB04xx

●Whole Circuit (Vout1=1.5V, Vout2=3.3V, fosc=1MHz, EN1 · 2 Pull-up Inside)

Ta=25°C SYMBOL MAX. UNITS CIRCUIT PARAMETER CONDITIONS MIN. TYP. 950 1500 Supply Current 1 V<sub>OUT1</sub>=V<sub>OUT2</sub>=Setting Voltage x 0.9 6 **I**DD1 μA V<sub>OUT1</sub>=V<sub>OUT2</sub>=Setting Voltage x 1.1 (Oscillation stops) 75 145 6 Supply Current 2 IDD2 \_ μA  $V_{EN1}=V_{EN2}=0V$ Stand-by Current Isтв 18 33 6 μA **UVLO Detect Voltage** VUVLOF VIN voltage which VOUT1=0V and LX pin becomes "L" (\*1) V 2 2.4 2.7 3.0 **UVLO Release Voltage** VUVLOR V<sub>IN</sub> voltage which V<sub>OUT1</sub>=0V and LX pin becomes "H" (\*1) --3.5 V 2 Thermal Shutdown TTSD 150 °C \_ Temperature Thermal Shutdown °C THYS 20 \_ Hysteresis Width

Test Conditions :

\*  $P_V_{DD1}$  · 2 stands for  $P_V_{DD1}=P_V_{DD2}$

\*\*Unless otherwise stated, P\_V<sub>DD1 · 2</sub>=5V, V<sub>EN1</sub>=V<sub>EN2</sub>= P\_V<sub>DD1 · 2</sub>

\*\*\* A\_V<sub>SS</sub>=P\_V<sub>SS1</sub>=P\_V<sub>SS2</sub>=0V

NOTE :

\*1 : "H" is judged "H">V<sub>IN</sub>-0.1V, "L" is judged "L"<0.1V

## ELECTRICAL CHARACTERISTICS (Continued)

#### XC9515BA06xx

| PARAMETER                         | SYMBOL                                 | CONDITIONS                                                                                                                                                        | MIN.             | TYP.     | MAX.            | UNITS | CIRCUIT |

|-----------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-----------------|-------|---------|

| Input Voltage                     | Vin                                    |                                                                                                                                                                   | 2.5              | -        | 5.5             | V     |         |

| Output Voltage1                   | Vout1                                  | Connected to the external components,<br>$P_V_{DD1\cdot 2}=V_{EN1}, V_{EN2}=0V$<br>$I_{OUT1}=30mA$                                                                | 1.470            | 1.500    | 1.530           | v     | 1       |

| Output Voltage2                   | Vout2                                  | Connected to the external components,<br>$P_V_{DD1\cdot2}=V_{EN2}, V_{EN1}=0V$<br>$I_{OUT2}=30mA$                                                                 | 3.234            | 3.300    | 3.366           | V     | 1       |

| Maximum Output Current 1 • 2 (*1) | IOUTMAX1<br>IOUTMAX2                   |                                                                                                                                                                   | 800              | -        | -               | mA    | 1       |

| Current Limit 1-2                 | ILIM1, ILIM 2                          |                                                                                                                                                                   | 1000             | -        | -               | mA    | 2       |

| Oscillation Frequency             | f <sub>osc</sub>                       | Connected to the external components, $I_{\text{OUT}}$ =10mA                                                                                                      | 0.85             | 1.00     | 1.15            | MHz   | 1       |

| Maximum Duty Cycle                | D <sub>MAX</sub>                       | V <sub>OUT1</sub> =V <sub>OUT2</sub> =0V                                                                                                                          | 100              | -        | -               | %     | 2       |

| Minimum Duty Cycle                | D <sub>MIN</sub>                       | V <sub>OUT1</sub> =V <sub>OUT2</sub> =V <sub>IN</sub>                                                                                                             | -                | -        | 0               | %     | 2       |

| Efficiency 1 (*2)                 | EFFI1                                  | Connected to the external components,<br>$P_V_{DD1\cdot2}=V_{EN1}=5.0V, V_{EN2}=0V$<br>$V_{OUT1}=1.5V, I_{OUT1}=200mA$                                            | -                | 89       | -               | %     | 1       |

| Efficiency 2 (*2)                 | EFFI2                                  | Connected to the external components,<br>$P_V_{DD1\cdot2}=V_{EN2}=5.0V$ , $V_{EN1}=0V$<br>$V_{OUT2}=3.3V$ , $I_{OUT2}=200mA$                                      | -                | 94       | -               | %     | 1       |

| LX1.2 "H" ON Resistance           | Rlx1h, Rlx2h                           | $V_{OUT1}=V_{OUT2}=0V$ , $I_{Lx1}=I_{Lx2}=100mA^{(*3)}$                                                                                                           | -                | 0.35(*4) | -               | Ω     | 3       |

| LX1-2 "L" ON Resistance           | Rlx1l, Rlx2l                           |                                                                                                                                                                   | -                | 0.35(*4) | -               | Ω     | -       |

| Integral Latch Time 1 · 2         | tlat1, tlat2                           | LX1 and LX2 are pulled down by a resistor of 200 $\Omega$<br>V <sub>OUT1</sub> = Setting Voltage × 0.9, V <sub>OUT2</sub> = Setting Voltage × 0.9 <sup>(*5)</sup> | -                | 6        | -               | ms    | Ī       |

| Soft-Start Time 1-2               | tSS1, tSS2                             | Time until EN1, EN2 or both pins changes from 0V to $V_{IN}$ and voltage becomes $V_{OUT1\cdot 2} \times 0.95$ , $I_{OUT1\cdot 2}=10mA$                           | -                | 1.3      | -               | ms    | 1       |

| EN1·2 "H" Voltage                 | Ven1h, Ven2h                           | $V_{\text{OUT1}}{=}V_{\text{OUT2}}{=}0V$ Voltage which LX1 or LX2 becomes "H" $^{(*6)}$                                                                           | 1.2              | -        | V <sub>IN</sub> | V     | 4       |

| EN1·2 "L" Voltage                 | VEN1L, VEN2L                           | $V_{\text{OUT1}}{=}V_{\text{OUT2}}{=}0V$ Voltage which LX1 or LX2 becomes "L" $^{(*6)}$                                                                           | AV <sub>SS</sub> | -        | 0.4             | V     | 4       |

| EN1 · 2 "H" Current               | I <sub>en1H</sub> , I <sub>en2H</sub>  | $P_V_{DD1.2} = V_{EN1} = V_{EN2} = 5.5V$                                                                                                                          | -                | -        | 0.1(*8)         | μA    | 4       |

| EN1 · 2 "L" Current               | I <sub>en1L</sub> , I <sub>en2L</sub>  | P_V <sub>DD1·2</sub> =5.5V, V <sub>EN1</sub> =V <sub>EN2</sub> =0V                                                                                                | -0.1(*8)         | -        | -               | μA    | 4       |

| LX1·2 "H" Leak Current (*7)       | $I_{leak1H},I_{leak2H}$                | $P_V_{DD1}$                                                                                                                                                       | -                | -        | 1.0(*9)         | μA    | 4       |

| LX1-2 "L" Leak Current            | $I_{\text{leak1L}}, I_{\text{leak2L}}$ | $P_V_{DD1.2}$ =5.5V, $V_{LX1}$ = $V_{LX2}$ = $V_{EN1}$ = $V_{EN2}$ =0V                                                                                            | -3.0(*9)         | -        | -               | μA    | 4       |

Test Conditions :

\*  $P_V_{DD1 \cdot 2}$  stands for  $P_V_{DD1}=P_V_{DD2}$ \*\*Unless otherwise stated,  $P_V_{DD1 \cdot 2}=5V$ ,  $V_{EN1}=V_{EN2}=P_V_{DD1 \cdot 2}$ \*\*\*  $A_V_{SS}=P_V_{SS1}=P_V_{SS2}=0V$

NOTE :

\*1 : When the difference between the input and the output is small, some cycles may be skipped completely before current maximizes.

If current is further pulled from this state, output voltage will decrease because of P-ch driver ON resistance.

\*2 : EFFI = { ( output voltage x output current ) / ( input voltage x input current) } x 100

\*3 : On resistance (Ω)= (V<sub>IN</sub> - Lx pin measurement voltage) / 100mA

\*4 : Designed value.

\*5 : Time until it short-circuits LX1 (LX2 in the side of 2CH) with GND via 1Ωof resistor from an operational state and is set to Low level from current limit pulse generating.

\*6 : "H" is judged as "H">V $_{\rm IN}$ -0.1V, "L" is judged as "L"<0.1V.

\*7 : When temperature is high, a current of approximately 20µA (maximum) may leak.

\*8 : Current which EN1 and EN2 are measured separately.

\*9 : Lead current which LX1 and LX2 are measured separately.

# ■ ELECTRICAL CHARACTERISTICS (Continued)

#### XC9515BA06xx

| AC9515BA00XX                                 |                         |                                                                         |                       |      |                 |       |         |  |  |

|----------------------------------------------|-------------------------|-------------------------------------------------------------------------|-----------------------|------|-----------------|-------|---------|--|--|

| ●VD (MR pin is) internally floating Ta=25 °C |                         |                                                                         |                       |      |                 |       |         |  |  |

| PARAMETER                                    | SYMBOL                  | CONDITIONS                                                              | MIN.                  | TYP. | MAX.            | UNITS | CIRCUIT |  |  |

| Detect Voltage                               | V <sub>DF(E)</sub> (*1) |                                                                         | 2.94                  | 3.00 | 3.06            | V     | 5       |  |  |

| Hysteresis Width                             | VHYS                    | $V_{HYS} = \{V_{DR(E)}   ^{(*2)} - V_{DF(E)} \} / V_{DF(E)} \times 100$ | -                     | 5.0  | -               | %     | -       |  |  |

| VD Output Current                            | Idout                   | $P_V_{DD1\cdot 2}=V_{DF}$ -0.01V, Apply 0.5V to $V_{DOUT}$              | 5.0                   | 6.6  | 8.0             | mA    | 4       |  |  |

| Delay Resistance                             | Rdly                    |                                                                         | -                     | 2.5  | -               | MΩ    | -       |  |  |

| MR "H" Level Voltage                         | Vmr                     | V <sub>DOUT</sub> ="H" Level Voltage (*3)                               | 1.2                   | -    | V <sub>IN</sub> | V     | 4       |  |  |

| MR "L" Level Voltage                         | Vmr                     | V <sub>DOUT</sub> ="L" Level Voltage (*3)                               | AV <sub>ss</sub>      | -    | 0.4             | V     | 4       |  |  |

| MR "H" Level Current                         | Imr                     | P_V <sub>DD1·2</sub> =MR=5.5V                                           | -                     | -    | 0.1             | μA    | 4       |  |  |

| MR "L" Level Current                         | Imr                     | P_V <sub>DD1·2</sub> =5.5V,MR=0V                                        | -0.1 <sup>(* 8)</sup> | -    | -               | μA    | 4       |  |  |

Test Conditions :

\*  $P\_V_{\text{DD1}+2}$  stands for  $P\_V_{\text{DD1}}\text{=}P\_V_{\text{DD2}}$

\*\*Unless otherwise stated, P\_V\_DD1  $\cdot$  \_2=5V, V\_EN1=V\_EN2= P\_V\_DD1  $\cdot$  \_2 \*\*\* A\_V<sub>SS</sub>=P\_V<sub>SS1</sub>=P\_V<sub>SS2</sub>=0V

NOTE :

\*1 :  $V_{DF(E)}$ =Detect Voltage

\*2 :  $V_{DR(E)}$ =Release Voltage

\*3 : "H" is judged as "H">V $_{\text{IN}}$ -0.1V, "L" is judged as "L"<0.1V

#### XC9515BA01xx

| ●Whole Circuit (V <sub>OUT1</sub> =1.5V, V <sub>OUT2</sub> =3.3V, f <sub>OSC</sub> =1MHz, EN1 and EN2 pins are internally floating) Ta=25 °C |        |                                                                                               |      |      |      | Ta=25 °C |         |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------|------|------|------|----------|---------|

| PARAMETER                                                                                                                                    | SYMBOL | CONDITIONS                                                                                    | MIN. | TYP. | MAX. | UNITS    | CIRCUIT |

| Supply Current 1                                                                                                                             | IDD1   | V <sub>OUT1</sub> =V <sub>OUT2</sub> = Setting Voltage × 0.9                                  | -    | 950  | 1500 | μA       | 6       |

| Supply Current 2                                                                                                                             | IDD2   | V <sub>OUT1</sub> =V <sub>OUT2</sub> = Setting Voltage × 1.1 (Oscillation stops)              | -    | 75   | 145  | μA       | 6       |

| Stand-by Current                                                                                                                             | Istb   | EN1=EN2=0V                                                                                    | -    | 5.5  | 11   | μA       | 6       |

| UVLO Detect Voltage                                                                                                                          | VUVLOF | $V_{\text{IN}}$ voltage which $V_{\text{OUT1}}{=}0V$ and $L_X$ pin becomes "L" $^{(*1)}$      | 1.5  | 1.8  | 2.1  | V        | 2       |

| UVLO Release Voltage                                                                                                                         | Vuvlor | $V_{\text{IN}}$ voltage which $V_{\text{OUT1}}\text{=}0V$ and $L_X$ pin becomes "H" $^{(*1)}$ | -    | I    | 2.3  | V        | 2       |

| Thermal Shutdown<br>Temperature                                                                                                              | Ttsd   |                                                                                               | -    | 150  | -    | °C       | -       |

| Thermal Shutdown<br>Hysteresis Width                                                                                                         | Thys   |                                                                                               | -    | 20   | -    | °C       | -       |

Test Conditions :

\* P\_V\_{DD1 \cdot 2} stands for P\_V\_{DD1}=P\_V\_{DD2}

\*\*Unless otherwise stated, P\_V<sub>DD1 · 2</sub>=5V, V<sub>EN1</sub>=V<sub>EN2</sub>= P\_V<sub>DD1 · 2</sub>

\*\*\* A\_V<sub>SS</sub>=P\_V<sub>SS1</sub>=P\_V<sub>SS2</sub>=0V

NOTE :

\*1 : "H" is judged "H">V<sub>IN</sub>-0.1V, "L" is judged "L"<0.1V

### ■TYPICAL APPRICATION CIRCUIT

<Example of the External Components>

L1 : 4.7 μ H(CDRH4D28C, SUMIDA)

- L2 :  $4.7 \,\mu$  H(CDRH4D28C, SUMIDA)

- $C_{IN1}$  : 10  $\mu$  F(ceramic)

- $C_{IN2}$  : 10  $\mu$  F(ceramic)

- $C_{L1}$  : 10  $\mu$  F(ceramic)

- $C_{L2}$  : 10  $\mu$  F(ceramic)

- RUP :  $100k\Omega$

### ■OPERATIONAL EXPLANATION

XC9515 series consists of a reference voltage source, ramp wave circuit, error amplifier, PWM comparator, phase compensation circuit, output voltage adjustment resistors, P-channel driver transistor, N-channel synchronous switching transistor, current limit circuit, UVLO circuit and others. The series ICs compare, using the error amplifier, the voltage of the internal voltage reference source with the feedback voltage from V<sub>OUT</sub> pin through split resistors, R<sub>FB1</sub> and R<sub>FB2</sub>. Phase compensation is performed on the resulting error amplifier output, to input a signal to the PWM comparator to determine the turn-on time during PWM operation. The PWM comparator compares, in terms of voltage level, the signal from the error amplifier with the ramp wave from the ramp wave circuit, and delivers the resulting output to the buffer driver circuit to cause the Lx pin to output a switching duty cycle. This process is continuously performed to ensure stable output voltage.

The current feedback circuit monitors the P-channel driver transistor current for each switching operation, and modulates the error amplifier output signal to provide multiple feedback signals. This enables a stable feedback loop even when a low ESR capacitor, such as a ceramic capacitor, is used, ensuring stable output voltage.

#### <Reference Voltage Source>

The reference voltage source provides the reference voltage to ensure stable output voltage of the DC/DC converter.

#### <Ramp Wave Circuit>

The ramp wave circuit determines switching frequency. The frequency is fixed internally at 1MHz. Clock pulses generated in this circuit are used to produce ramp waveforms needed for PWM operation, and to synchronize all the internal circuits.

#### <Error Amplifier>

The error amplifier is designed to monitor output voltage. The amplifier compares the reference voltage with the feedback voltage divided by the internal split resistor,  $R_{FB1}$  and  $R_{FB2}$ . When a voltage lower than the reference is fed back, the output voltage of the error amplifier increases. The gain and frequency characteristics of the error amplifier output are fixed internally to deliver an optimized signal to the mixer.

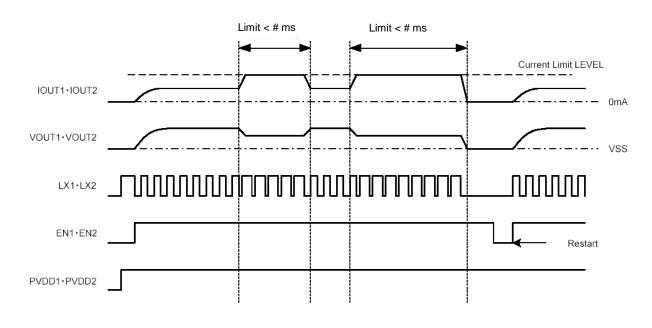

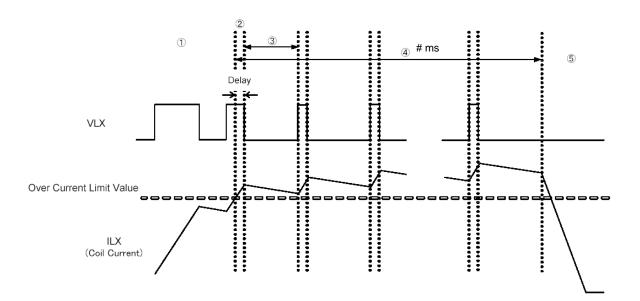

#### <Current Limit>

The current limiter circuit of the XC9515 series monitors the current flowing through the P-channel MOS driver transistor connected to the Lx pin, and features a combination of the current limit mode and the latch mode.

- (1) When the driver current is greater than a specific level (peak value of coil current), the current limit function operates to off the pulses from the Lx pin at any giving timing.

- 2When the driver transistor is turned off, the limiter circuit is then released from the current limit detection state.

- ③At the next pulse, the driver transistor is turned on. However, the transistor is immediately turned off in the case of an over current state.

- (4) When the over current is eliminated, the IC resumes its normal operation.

The IC waits for the over current state to end by repeating the steps ① to ③. If an over current state continues for a few ms and the above three steps are repeatedly performed, the IC performs the function of latching the OFF state of the driver transistor. Both two DC/DC blocks stop operations when either CH1 or CH2 of protection circuit is activated. At this time, both Lx1 and Lx2 become high impedance. Once the IC is in latch mode, operations can be resumed by either turning the IC off after letting EN1 and EN2 pins down to low level, or by restoring power. (For restoring power, the IC should be turned off after P\_V\_{DD1} and P\_V\_{DD2} voltages drop below the low level of EN1 and EN2 pin.)

The latch operation can be released from the current limit detection state because of the circuit's noise. Also, depending on the state of the PC Board, latch time may become longer and latch operation may not work. In order to avoid the effect of noise, the board should be laid out so that capacitors are placed as close to the chip as possible.

### OPERATIONAL EXPLANATION (Continued)

#### <Thermal Shutdown>

For protecting the IC from heat damage, the thermal shutdown circuit monitors the chip temperature. When the chip temperature reaches 150°C, the thermal shutdown circuit operates and the driver transistor will be set to OFF. As the chip temperature drops to 130°C by stopping current flow, the soft-start function operates to turn the output on.

#### <Short-Circuit Protection>

The short-circuit protection circuit monitors the FB voltage. If the output is shorted incorrectly with the ground, the short-circuit protection circuit operates and turns the driver transistor off to latch when the FB voltage becomes less than half of the setting voltage. Both two DC/DC blocks stop operations when either CH1 or CH2 of protection circuit is activated. At this time, both Lx1 and Lx2 become high impedance. Once the IC is in latch mode, operations can be resumed by either turning the IC off after letting both ends of EN1 and EN2 pins down to low level, or by restoring power. (The P\_V<sub>DD1</sub> and P\_V<sub>DD2</sub> voltages should be less than the low level of the EN1 and EN2 pins when restoring power.)

#### <Soft Start Function>

The soft-start circuit protects against inrush current, when the power is switched on, and also to protect against voltage overshoot. It should be noted, however, that this circuit does not protect the load capacitor (CL) from inrush current. With the Vref voltage limited and depending upon the input to the error amps, the operation maintains a balance between the two inputs of the error amps and controls duty so that it doesn't increase more than is necessary.

#### <UVLO Circuit>

When the VIN pin voltage becomes 1.8V (TYP.) or lower (for XC9515A, 2.7V or lower), the P-channel output driver transistor is forced OFF to prevent false pulse output caused by unstable operation of the internal circuitry. When the VIN pin voltage becomes 1.9V (TYP.) or higher (for XC9515A, 3.0V or lower), switching operation takes place. By releasing the UVLO function, the IC performs the soft-start function to initiate output startup operation.

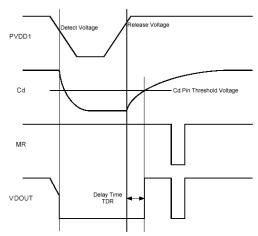

#### <Voltage Detector Block>

The series' detector function monitors the voltage divided by resistors connected to the P\_VDD1 pin, as well as monitoring the voltage of the internal reference voltage source via the comparator. Because of hysteresis at the detector function, output at the  $V_{DouT}$  pin will invert when the sense pin voltage of the detector block (P\_VDD1) increases above the release voltage (105% of the detect voltage). The output configuration of the  $V_{DouT}$  pin is N-channel open drain, therefore, a pull-up resistor is required. The voltage detector block has a manual reset (MR) pin. By setting the MR pin at low level, the  $V_{DouT}$  pin is forced to be at low level.

By connecting a capacitor (Cd) to the Cd pin, the XC9515 series can set a delay time to VDOUT pin's output signal when releasing voltage. The delay time can be calculated from the internal resistance, Rdelay (2.5M $\Omega$  fixed TYP.) and the value of Cd as per the following equation. As selecting the capacitor (Cd), the delay time can be set freely.

$t_{DR}$  (Delay time) =Cd x Rdelay x 0.69

| ●Release Delay               |                                           | Ta=25 °C                                         |

|------------------------------|-------------------------------------------|--------------------------------------------------|

| Delay Capacity Cd [ $\mu$ F] | Release Delay t <sub>DR</sub> (TYP.) [ms] | Release Delay t <sub>DR</sub> (MIN. ~ MAX.) [ms] |

| 0.01                         | 17                                        | 10 ~ 24                                          |

| 0.022                        | 38                                        | 23 ~ 53                                          |

| 0.047                        | 81                                        | 49 ~ 113                                         |

| 0.1                          | 173                                       | 103 ~ 242                                        |

| 0.22                         | 380                                       | 228 ~ 532                                        |

| 0.47                         | 811                                       | 487 ~ 1135                                       |

| 1                            | 1725                                      | 1035 ~ 2415                                      |

### NOTES ON USE

- 1. Please use this IC within the stated maximum ratings. The IC is liable to malfunction should the ratings be exceeded.

- Please apply the same electrical potential to the P\_V<sub>DD1</sub> and P\_V<sub>DD2</sub> pins. Even where either CH1 or CH2 is used, both P\_V<sub>DD1</sub> and P\_V<sub>DD2</sub> pins should have the same electrical potential. Applying the electrical potential to only one side causes malfunction. Also the same electrical potential should be applied to the P\_V<sub>SS1</sub>, P\_V<sub>SS2</sub> and A\_V<sub>SS</sub> pins.

- 3. The XC9515 series is designed for use with ceramic output capacitors. If, however, the potential difference between dropout voltage or output current is too large, a ceramic capacitor may fail to absorb the resulting high switching energy and the output could be unstable. If the input-output potential difference is large, use a larger output capacitor to compensate for insufficient capacitance.

- 4. When the peak current, which exceeds limit current flows within the specified time, the built-in driver transistor is turned off (the integral latch circuit). During the time until it detects limit current and before the built-in transistor can be turned off, the current for limit current flows; therefore, care must be taken when selecting the rating for the coil.

- 5. When the input voltage is low, limit current may not be reached because of voltage falls caused by ON resistance or serial resistance of the coil.

- 6. Since the potential difference for input voltage has occurred to the both ends of a coil, the time changing rate of the coil current is large when the P-channel driver transistor is ON. On the other hand, since the V<sub>OUT</sub> pin short-circuits to the GND when the N-channel transistor is ON and there is almost no potential difference of the coil both ends, the time changing rate of the coil current becomes very small.

This operation is repeated and the delay time of the circuit also influences, therefore, the coil current is converged on the current value beyond the amount of current which should be restricted essentially.

The short-circuit protection does not operate during the soft-start time. As soon as the soft-start time finishes, the short-circuit protection starts to operate and the circuit becomes disable.

The delay time of the circuit also influences when step-down ratio is large, as the result, a current more than over current limit may flow. Please do not exceed the absolute maximum ratings of the coil.

- ① A current flows to the driver transistor up to the current limit (ILIM).

- Por the delay time of the circuit, a current more than the ILIM flows after the ILIM decide until the P channel driver transistor turns off.

- ③ Time changing rate of the coil current becomes very small because there is no potential difference between both ends of the coil.

- ④ The Lx pin oscillates a narrow pulse during the soft-start time because of the current limit.

- 5 The circuit is latched since the short-circuit protection operates and the P-channel driver transistor is turned off.

### ■NOTES ON USE (Continued)

- 7. Driving current below the minimum operating voltage may lead malfunction to the UVLO circuit because of the noise.

- 8. Depending on the PC board condition, the latch function may be released from limit current detection state and the latch time may extend or fail to reach the latch operation. Please locate the input capacitance as close to the IC as possible.

- 9. Spike noise and ripple voltage arise in a switching regulator as with a DC/DC converter. These are greatly influenced by external component selection, such as the coil inductance, capacitance values, and board layout of external components. Once the design has been completed, verification with actual components should be done.

- 10. With the DC/DC converter block of the IC, the peak current of the coil is controlled by the current limit circuit. Since the peak current increases when dropout voltage or load current is high, current limit starts operating, and this can lead to instability. When peak current becomes high, please adjust the coil inductance value and fully check the circuit operation. In addition, please calculate the peak current according to the following formula:

Peak current:  $lpk = (VIN - V_{OUT}) \times OnDuty / (2 \times L \times fosc) + I_{OUT}$ L: Coil Inductance Value, fosc: Oscillation Frequency

- 11. When the load current is light in PWM control, very narrow pulses will be outputted, and there is the possibility that some cycles may be skipped completely.

- 12. When the difference between VIN and VOUT is small, and the load current is heavy, very wide pulses will be outputted and there is the possibility that some cycles may be skipped completely.

- 13. If the power input pin voltage is assumed to decrease rapidly (ex. from 6.0V to 0V) at the release of the operation although delay capacitance (Cd) pin is connected, please connect an Shottky barrier diode between the power input (P\_V<sub>DD1</sub>) pin and the delay capacitance (Cd) pin.

- 14. Please connect a pull-up resistor with 100 to  $200k\Omega$  to the output pin of the voltage detector block (V<sub>DOUT</sub>).

- 15. The delay time of the voltage detector block in heavy load may extend because of the noise of the DC/DC block. Precipitous and large voltage fluctuation at the power input pin may cause malfunction of the IC.

- 16. Use of the IC at voltages below the minimum operating voltage may lead the output voltage drop before achieving over current limit.

- 17. When P\_VDD1 and P\_VDD2 power supply pins and EN1 and EN2 enable pins are in undefined states, the latch protection circuit may not be reset so that the IC operation does not start correctly. Power supply and enable pins (EN1,EN2) should be grounded before starting the IC operation.

- 18.

[Undefined state conditions for each pin]  $P_V_{DD1}=P_V_{DD}2=0.1V \sim 1.2V$  $V_{EN1}=V_{NE2}=0.4V \sim 1.2V$

- 19. UVLO function works even if when V<sub>IN</sub> input voltage falls below the UVLO voltage in very short time period like a few ten nanoseconds.

- Instruction on Pattern Layout

- 1. In order to stabilize VIN's voltage level, we recommend that a by-pass capacitor (CIN1 and CIN2) be connected as close as possible to the P\_V<sub>DD1</sub> P\_V<sub>DD2</sub> pins and P\_V<sub>SS1</sub> P\_V<sub>SS2</sub> pins.

- 2. Please mount each external component as close to the IC as possible.

- 3. Wire external components as close to the IC as possible and use thick, short connecting traces to reduce the circuit impedance.

- 4. Make sure that the V<sub>SS</sub> traces are as thick as possible, as variations in the V<sub>SS</sub> potential caused by high V<sub>SS</sub> currents at the time of switching may result in instability of the DC/DC converter.

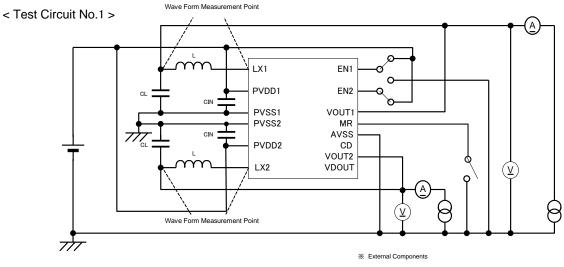

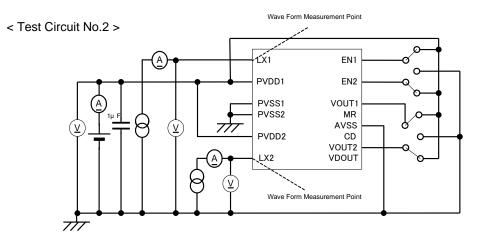

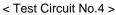

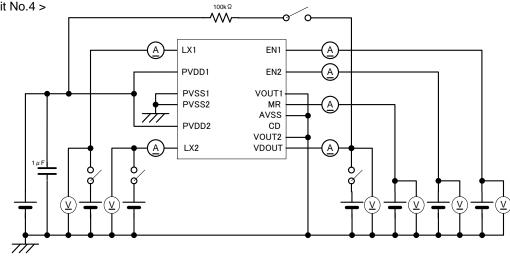

## ■TEST CIRCUITS

$\begin{array}{ll} L & : 4.7 \mu \mbox{ H(CDRH4D28C}: \mbox{SUMIDA}) \\ CIN & : 10 \mu \mbox{ F} \mbox{ (ceramic)} \\ CL & : 10 \mu \mbox{ F} \mbox{ (ceramic)} \end{array}$

< Test Circuit No.3 >

# ■TEST CIRCUITS (Continued)

TOIREX 15/21

# ■TYPICAL PERFORMANCE CHARACTERISTICS

#### (1) Efficiency vs. Output Current

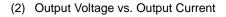

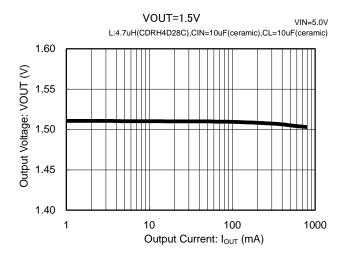

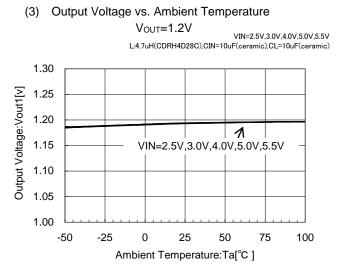

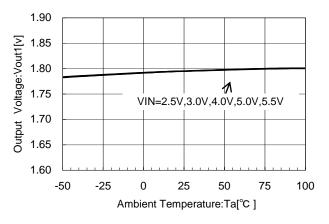

## ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(4) Oscillation Frequency vs. Ambient Temperature

VIN=4.0V.5.0V.5.5V

TOIREX 17/21

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

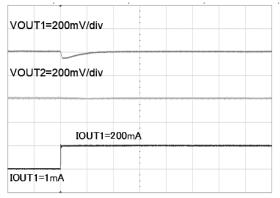

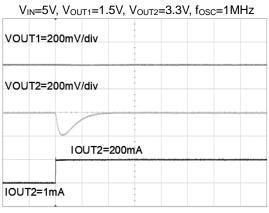

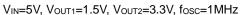

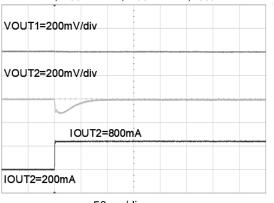

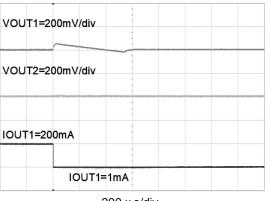

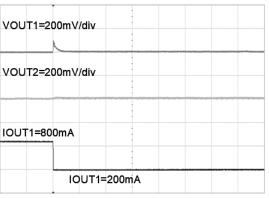

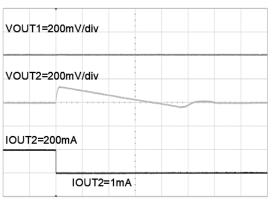

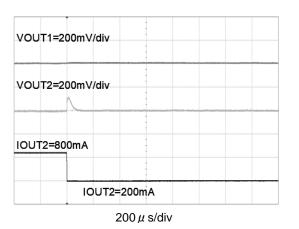

#### (5) Load Transient Response

VIN=5V, VOUT1=1.5V, VOUT2=3.3V, fosc=1MHz

$50\,\mu\,\mathrm{s/div}$

VIN=5V, VOUT1=1.5V, VOUT2=3.3V, fosc=1MHz

| VOUT1=200mV/div |  |

|-----------------|--|

| VOUT2=200mV/div |  |

|                 |  |

| IOUT1=800mA     |  |

|                 |  |

| IOUT1=200mA     |  |

$50\,\mu\,\mathrm{s/div}$

50 µ s/div

$50\,\mu\,\mathrm{s/div}$

200 µ s/div

$200\,\mu\,\mathrm{s/div}$

$200\,\mu\,\mathrm{s/div}$

# ■ PACKAGING INFORMATION

For the latest package information go to, www.torexsemi.com/technical-support/packages

| PACKAGE           | OUTLINE / LAND PATTERN | THERMAL CHARACTERISTICS  |

|-------------------|------------------------|--------------------------|

| QFN-20 QFN-20 PKG |                        | QFN-20 Power Dissipation |

### ■MARKING RULE

#### ●QFN-20

QFN-20 (TOP VIEW)

#### Standard Product

123 represent product series

| MARK |   |   |                |  |

|------|---|---|----------------|--|

| 1    | 2 | 3 | PRODUCT SERIES |  |

| 5    | 1 | 5 | XC9515*****-G  |  |

#### ④Input Voltage Range, UVLO Voltage

| MARK | PRODUCT SERIES | OPTIONAL FUNCTIONS                                         |

|------|----------------|------------------------------------------------------------|

| A    | XC9515A****-G  | Input Voltage Range 5V±10%, UVLO<br>Voltage 2.7V (TYP.)    |

| В    | XC9515B****-G  | Input Voltage Range 2.5V~5.5V, UVLO<br>Voltage 1.8V (TYP.) |

#### 5 EN Pin, MR Pin, Internal Control

| PRODUCT SERIES | OPTIONAL FUNCTIONS                                                                                  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------|--|--|--|

|                | EN1, EN2 Pin Open                                                                                   |  |  |  |

| AC9515 A -G    | MR Pin Open                                                                                         |  |  |  |

|                | Built-in EN1, EN2 Pin Pull-up Resistance                                                            |  |  |  |

| XC9515"B"""-G  | Built-in MR Pin Pull-up Resistance                                                                  |  |  |  |

|                | EN1, EN2 Pin Open                                                                                   |  |  |  |

| XC9515 C -G    | Built-in MR Pin Pull-up Resistance                                                                  |  |  |  |

|                | Built-in EN1, EN2 Pin Pull-up Resistance                                                            |  |  |  |

| AC9515 D -G    | MR Pin Open                                                                                         |  |  |  |

|                | PRODUCT SERIES   XC9515*A****-G   XC9515*B****-G   XC9515*C****-G   XC9515*C****-G   XC9515*D****-G |  |  |  |

67 represents integer number of setting voltage

| MARK |                          | PRODUCT SERIES |

|------|--------------------------|----------------|

| 6    | $\overline{\mathcal{O}}$ | PRODUCT SERIES |

| 0    | 1                        | XC9515**01**-G |

89 represents production lot number

Order of 01, ...09, 10, 11, ...99, 0A, ...0Z, 1A, ...9Z, A0, ...Z9, AA, ...ZZ.

(G, I, J, O, Q, W excluded)

\*No character inversion used.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- 3. Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions. Do not use the product for the above use unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.